## E-PAPER 1.54" DISPLAY MODULE

Electronic paper is a display technology designed to mimics the appearance of ordinary ink on paper. Unlike a conventional flat panel display, which uses a backlight to illuminate it's pixels, electronic paper reflects light like ordinary paper. It is capable of holding text and images indefinitely without drawing electricity, while allowing the image to be changed later. To build e-paper, several different technologies exist, some using plastic substrate and electronics, so that display is flexible. E-paper has the potential to be more comfortable to read than conventional display. This is due to the stable image, which does not need to be refreshed constantly, the wider viewing angle, and the fact that it reflects ambient light rather than it's own light. An e-paper display can be read in direct sunlight without the image appearing to fade.

This is an E-Ink display module, 1.54 inch, 200x200 resolution, with embedded controller, communicating via SPI interface, supports partial refresh. E-paper also known as electronic Due to the advantages like ultra low power consumption, wide viewing angle, clear display without electricity, it is an ideal choice for applications such as shelf label, industrial instrument, and so on.

This product is an E-paper device adopting the image display technology of Microencapsulated Electrophoretic Display, MED. The initial approach is to create tiny spheres, in which the charged color pigments are suspending in the transparent oil and would move depending on the electronic charge. The E-paper screen display patterns by reflecting the ambient light, so it has no background light requirement. Under sunshine, the E-paper screen still has high visibility with a wide viewing angle of 180 degrees. It is the ideal choice for E-reading.

#### **FEATURES:**

- No backlight, keeps displaying last content for a long time even when power down

- Ultra low power consumption, basically power is only required for refreshing

- SPI interface, for connecting with controller boards like Raspberry Pi/Arduino/Nucleo, etc.

- Onboard voltage translator, compatible with 3.3V/5V MCUs

- Comes with development resources and manual (examples for Raspberry Pi/Jetson Nano/Arduino/STM32)

#### **SPECIFICATIONS:**

Operating voltage: 3.3V/5V

Interface: 3 -wire SPI, 4-wire SPI

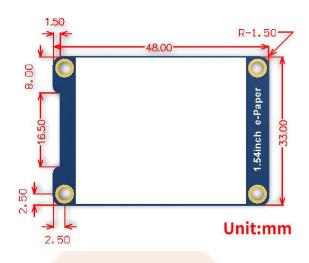

Outline dimension: 48mm × 33mm

Display size: 27.6mm × 27.6mm

Dot pitch: 0.138× 0.138

Resolution: 200 × 200

Display color: black, white

• Grey level: 2

Partial refresh time: 0.3sFull refresh time: 2s

Refresh power: 26.4mW(typ.)

Standby power: <0.017mW</li>

Viewing angle: >170°

#### **INTERFACE:**

| SYMBOL | DESCRIPTION                            |

|--------|----------------------------------------|

| VCC    | Power positive (3.3V power input)      |

| GND    | Ground                                 |

| DIN    | SPI MOSI pin                           |

| CLK    | SPI SCK pin                            |

| CS     | SPI chip selection, low active         |

| DC     | Data/command selection (high for data, |

|        | low for command                        |

| RST    | External reset pin (low for reset)     |

| BUSY   | Busy status output pin (low for busy)  |

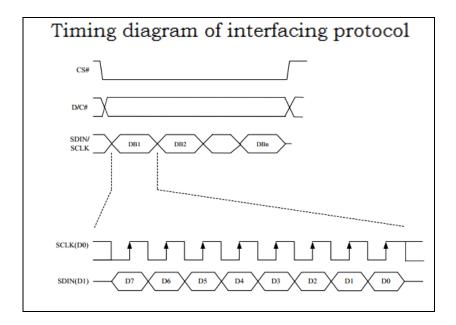

### **COMMUNICATION PROTOCOL:**

Note: Different from the traditional SPI protocol, the data line from the slave to the master is hidden since the device only has a display requirement.

CS is slave chip select, when CS is low, the chip is enabled.

DC is data/command control pin, when DC = 0, write command, when DC = 1, write data.

SCLK is the SPI communication clock

SDIN is the data line from the master to the slave in SPI communication.

SPI communication has data transfer timing, which is combined by CPHA and CPOL.

- 1. CPOL determines the level of the serial synchronous clock at idle state. When CPOL = 0, the level is Low. However, CPOL has little effect to the transmission.

- 2. CPHA determines whether data is collected at the first clock edge or at the second clock edge of serial synchronous clock; when CPHL = 0, data is collected at the first clock edge.

There are 4 SPI communication modes. SPI0 is commonly used, in which CPHL = 0, CPOL = 0.

As you can see from the figure above, data transmission starts at the first falling edge of SCLK, and 8 bits of data are transferred in one clock cycle. In here, SPI0 is in used, and data is transferred by bits, MSB first.

## **PACKAGE INCLUDE:**

- 1.54 inch e-Paper module x1

- PH.0 20 cm 8 pin x1

# **OUTER DIMENSION:**

# **APPLICATIONS:**

- Education: Digital school books

- Wristwatches

- E-Books

- Newspaper

- Cell phones

- Status display